# IMPEDANCE COMPENSATION

# I – INTRODUCTION

Impedance spectroscopy is a powerful analytical tool for the characterization of the electrical properties of materials. This characterization needs cables and/or sample holder to interface the Device Under Test (DUT) to the measuring instrument (Impedance analyzer, LCR, potentiostat, etc). The cables the sample holder introduce and/or additional impedances termed as "residual impedances". These additional impedances impact the measurement accuracy by an overestimation of the measured electrical properties of the DUT and so an overestimation of the relative contribution of individual processes (bulk, grain boundaries, interface, or electrode capacitances/resistances) involved in the electrical response of the DUT.

The residual impedances can be "eliminated" or compensated using a compensation procedure.

The aim of this note is to introduce impedance users to the capabilities of compensation for obtaining reliable and accurate measurements. It also explains why the compensation is needed and how to perform it. An example of compensation on a low capacitance capacitor that "mimics" a bulk capacitance is given here to illustrate the effect of compensation on the accuracy and reliability of impedance measurement.

# **II – THEORITICAL BACKGROUND**

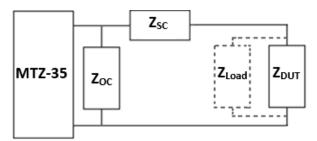

As mentioned above, cables and sample holder are sources of "stray" impedance affecting the accuracy of the measured impedance of the DUT. In order to "remove" these residual impedances a compensation procedure is needed [1]. This procedure is sometimes named "nulling" [2-3]. The compensation consists in performing at least one of the three processes below: 1- Open-circuit (OC) compensation to compensate for the Open-circuit residual impedance  $Z_{OC}$ . It consists in measuring the residual impedance  $Z_{OC}$  in parallel with the actual impedance  $Z_{DUT}$  of the DUT (Fig. 1)

2- Short-circuit (SC) compensation to compensate for the Short-circuit residual impedance  $Z_{SC}$ . It consists in measuring the residual impedance  $Z_{SC}$  in series with the actual impedance of the DUT (Fig. 1).

3- Load compensation compensates for complex effects within the cables and/or the sample holder mainly observed at high frequencies. It consists in measuring the impedance of a load  $Z_{\text{Load}}$  (Fig. 1).

Figure. 1 shows a scheme of the residual impedances  $Z_{OC}$ ,  $Z_{SC}$  and  $Z_{Load}$ .

Figure 1: Sketch of the residual impedances measured during impedance compensation.

## **II-1 OPEN & SHORT CIRCUIT COMPENSATION**

In general, the residual impedance can be seen as the sum of the two main residuals impedances: an OC residual impedance  $Z_{OC}$  and a short circuit residual impedance  $Z_{SC}$ .  $Z_{OC}$  corresponds mainly to the capacitance of the cables and/or the sample holder whereas  $Z_{SC}$  is mainly due to the inductance and the resistance of the cables. More details on the open-circuit and short-circuit compensation can be found in the technical note TN#1 [4].

Once  $Z_{OC}$  and  $Z_{SC}$  have been measured, the actual impedance of the sample  $Z_{DUT}$  is calculated as follows:

MMMM

$$Z_{\rm DUT} = \frac{Z_{\rm M} - Z_{\rm SC}}{1 - (Z_{\rm M} - Z_{\rm SC})/Z_{\rm OC}}$$

(1)

Where

- Z<sub>DUT</sub> the compensated (actual) impedance of DUT.

- *Z*<sub>OC</sub> the impedance measured at open-circuit.

- Z<sub>SC</sub> the impedance measured at short-circuit.

- $Z_{\rm M}$  the measured "raw" impedance of DUT.

## **II-2 LOAD COMPENSATION**

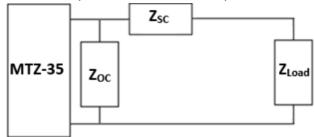

Load compensation is performed by replacing the DUT by a load which is an electronic component (high precision resistor or capacitor) with a known impedance value, preferably close to DUT's impedance [5]. This compensation is recommended for measurement performed at high frequencies. It is carried-out once the open-circuit and shortcircuit compensations have been performed.

Figure 2: Load impedance Z<sub>Load</sub>.

Once the impedance of the load has been measured, the actual impedance of the DUT can be computed using the following formula:

$$Z_{\text{DUT}} = \frac{Z_{\text{ref}}(Z_{\text{M}} - Z_{\text{SC}})(Z_{\text{OC}} - Z_{\text{Load}})}{(Z_{\text{OC}} - Z_{\text{M}})(Z_{\text{Load}} - Z_{\text{SC}})} \quad (2)$$

Where:

- *Z*<sub>OC</sub> the impedance measured at open-circuit.

- *Z*<sub>SC</sub> the impedance measured at short-circuit.

- $Z_{M}$  the measured "raw" impedance of DUT.

- Z<sub>Load</sub> the measured impedance of the load.

- Z<sub>ref</sub> the nominal impedance (resistance or capacitance) of the load. This value is given by the load's manufacturer or measured by a high precision instrument.

The three compensations (Open, Short & Load) are used to compensate for the residual

impedances. However only the open-circuit compensation is necessary. The short-circuit compensation (in addition to open-circuit compensation) is needed for DUTs with low impedance. For high frequencies measurements, the load compensation is also recommended.

## **III – EXPERIMENT**

In order to illustrate the effect of the compensation on the accuracy of the impedance measurement, a capacitor with a low capacitance of 100 pF was chosen as a DUT. A second test was performed on a second capacitor with a high capacitance of 10 nF. Its results are provided upon request.

Figure 3: 100 pF capacitor.

The capacitor was connected to MTZ-35 impedance analyzer using a real two terminal connection and two alligator clips [6]. This connection mode was chosen in order to perform the measurement at very high frequencies. The capacitor was installed in a Faraday cage in order to protect it from electromagnetic noise. The Faraday cage was then connected to the earth connector of the MTZ-35 (Fig. 4).

Figure 4: Experimental setup.

Marre

Science Instruments, 4 Rue de Vaucanson, 38170 Seyssinet-Pariset, FRANCE Tel: +33 476 98 68 31 – Fax: +33 476 98 69 09 <u>www.bio-logic.net</u>

The impedance measurements were performed in the frequency range of 30 MHz to 100 Hz by applying an AC voltage of  $V_{pp}$  = 100 mV.

Figure 5 shows the experimental settings used for measuring the impedance of the capacitor.

| Load Settings                                                          | 100 pF capacit      | or +FC            | ^                       |  |  |  |

|------------------------------------------------------------------------|---------------------|-------------------|-------------------------|--|--|--|

| Save Settings                                                          |                     |                   | ~ ·                     |  |  |  |

| Generate output File                                                   |                     |                   |                         |  |  |  |

| C:\Data\MT-Lab\Compensation\Test on 100 pF capacitor 30 MHz 101 Browse |                     |                   |                         |  |  |  |

|                                                                        |                     |                   |                         |  |  |  |

| Cell Factor<br>Radius [mm]<br>1>                                       | Area [mm²]<br>3.142 | Distance [mm]     |                         |  |  |  |

| Frequency Settings                                                     |                     |                   |                         |  |  |  |

| Type: 💿 Log                                                            | OLinear             |                   |                         |  |  |  |

| FStart [Hz]                                                            | FStop [Hz]          | Points per decade | Type of measure         |  |  |  |

| 30e6                                                                   | 100                 | 10                | 20 Cycles - Low_noise ∨ |  |  |  |

| Signal Amplitude                                                       |                     |                   |                         |  |  |  |

| Signal Amplitude                                                       | DC [V]              | AC [Vp]           |                         |  |  |  |

| Dielectric Mode                                                        | 0                   | 0.1               |                         |  |  |  |

| DC Biasing                                                             |                     |                   |                         |  |  |  |

| Start [V]                                                              | Stop [V]            | Number of Steps   | Pause [min : sec]       |  |  |  |

| 0                                                                      | 2                   | 10                | 0 : 0                   |  |  |  |

|                                                                        |                     |                   |                         |  |  |  |

| Gain                                                                   |                     |                   |                         |  |  |  |

| Current Shunt                                                          | Auto                |                   |                         |  |  |  |

|                                                                        | ~                   |                   |                         |  |  |  |

Figure 5: Experimental setting.

During the open-circuit compensation where no sample holder is used, the positive and the negative terminals of the cable have been separated before measuring the impedance at open-circuit.

In the case where a sample holder is used, open-circuit impedance is measured after separating the electrodes of the sample holder (after removing the DUT). The separation distance between the electrodes of the sample holder should be equal to the DUT thickness.

The short-circuit compensation consists in measuring the impedance when the positive and the negative terminals of the cable are shorted. In the case where a sample holder is used the electrodes of the sample holder have to be shorted. The Load compensation consists in measuring the impedance of a load (high precision capacitor or resistor). In our case (high frequencies measurement) a load compensation was performed. It consisted in measuring the impedance of a 10 nF capacitor (load). The three compensations were repeated to check the reproducibility of measurement.

# **IV – RESULTS**

## **IV-1 IMPEDANCE OF THE DUT**

The impedance of the 100 pF capacitor was measured using 2-point setup.

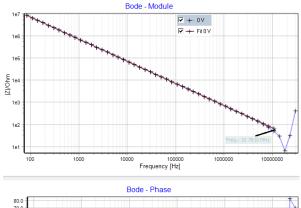

Figure 6 shows the obtained impedance data (without compensation). The Bode diagram shows an impedance plot typical to a pure capacitor.

Figure 6: Bode diagram of 100 pF capacitor impedance.

The impedance plot was fitted to a pure capacitor with a capacitance of 223 pF (Fig. 7).

Marre

Science Instruments, 4 Rue de Vaucanson, 38170 Seyssinet-Pariset, FRANCE Tel: +33 476 98 68 31 – Fax: +33 476 98 69 09 <u>www.bio-logic.net</u>

| ✓ Y ZFit - Bio-Logic ×                  |  |  |  |  |

|-----------------------------------------|--|--|--|--|

| Inputs                                  |  |  |  |  |

| 🗌 Multi files 🛛 🖶 🚔                     |  |  |  |  |

| Select current v cycle                  |  |  |  |  |

| Equivalent circuit selection            |  |  |  |  |

| C1 ~                                    |  |  |  |  |

| Edit Load Save                          |  |  |  |  |

| Fit                                     |  |  |  |  |

| Results                                 |  |  |  |  |

| param. sel sign value unit              |  |  |  |  |

| C1 V + 0,223 6e-9 F                     |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

|                                         |  |  |  |  |

| <u>P</u> seudoC                         |  |  |  |  |

| $\chi^2$ 22,87e9 $\chi/\sqrt{N}$ 21 178 |  |  |  |  |

| χ <sup>2</sup> /  Z  32,17 Cycle 1      |  |  |  |  |

| Iterations 5000 (Randomize)             |  |  |  |  |

| Calculate Minimize Stop Copy Close      |  |  |  |  |

Figure 7: ZFit window of uncompensated measurement.

The measured capacitance is higher than the nominal value (100 pF) provided by the manufacturer. The "offset capacitance" (123 pF) corresponds to the residual capacitance due to cables. Indeed, the MTZ-35 impedance analyzer is calibrated up to the BNC connectors (front panel) of the MTZ-35. The cables used to connect the capacitor generate a residual impedance (capacitance). In order to eliminate this residual impedance due to the cables a compensation is needed.

#### **IV-2 COMPENSATION**

The compensation described in this note is complementary to that performed with MT-Lab software which was detailed in the technical note TN#1 [4]. This compensation, available in EC-Lab software, is compatible with data provided by EC-Lab and MT-Lab software. It is a fast post-process method where the actual impedance of the DUT is computed using the equation (1) or (2).

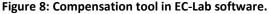

In this example, the open-circuit, short-circuit and load impedance data were acquired separately by MT-Lab software connected to MTZ-35. The load compensation was performed using a capacitor with a nominal capacitance of 10 nF. In the compensation window of EC-Lab software, a 10 nF value was set in  $Z_{ref}$  box (Fig. 9)

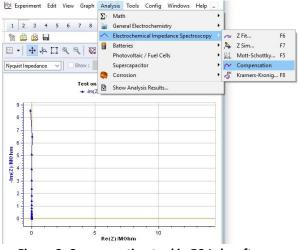

For computing the actual impedance of the DUT, the user has to open EC-Lab software, select "Analysis" menu, impedance spectroscopy and "Compensation" tool (Fig. 8).

The impedance of DUT, the open-circuit, short-circuit and load impedance files are loaded in the compensation window (Fig. 9). The user has to select "fra" extension in the open window in order to be able to load the four files in the compensation window.

Figure 9: OC & SC and load compensation window.

Malle

Science Instruments, 4 Rue de Vaucanson, 38170 Seyssinet-Pariset, FRANCE Tel: +33 476 98 68 31 – Fax: +33 476 98 69 09 <u>www.bio-logic.net</u>

MT-Lab/EC-Lab – Application Note #04 02/2019

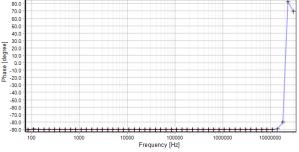

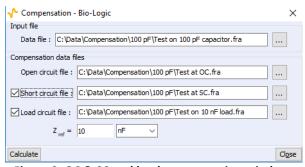

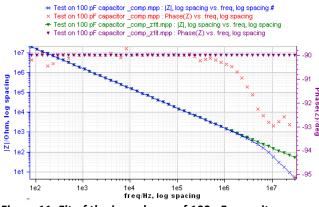

Once we click on "Calculate" button the computed data file is generated. This file has the same filename as the uncompensated data file with a "\_comp" suffix and a mpp extension. Figure 10 shows the Bode diagram of the compensated data.

Figure 10: Bode plot of the impedance of 100 pF capacitor after compensation.

The compensated data was fitted to a pure capacitor with a capacitance value of **98.9 pF** (Fig. 11 & 12).

Figure 11: Fit of the impedance of 100 pF capacitor after compensation.

| ✓ ZFit - Bio-Logic                         | × |  |  |  |  |

|--------------------------------------------|---|--|--|--|--|

| Inputs                                     |   |  |  |  |  |

| Multi files 🖶 🛶 🙀                          | è |  |  |  |  |

|                                            | ] |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

| Select current v cycle                     |   |  |  |  |  |

| Equivalent circuit selection               |   |  |  |  |  |

| C1 ~                                       |   |  |  |  |  |

| Edit Load Save                             | _ |  |  |  |  |

| Fit                                        |   |  |  |  |  |

| Besults                                    | * |  |  |  |  |

| param. sel. sign value unit                | - |  |  |  |  |

| C1 ✔ + 98,9e-12 F                          |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

|                                            |   |  |  |  |  |

| <u>P</u> seudoC                            |   |  |  |  |  |

| $\chi^2$ 0,125 5e12 $\chi/\sqrt{N}$ 49 615 |   |  |  |  |  |

| χ <sup>2</sup> / [Z] 184,5 Cycle 1         |   |  |  |  |  |

| Iterations 5000 (Randomize)                |   |  |  |  |  |

| Calculate Minimize Stop Copy Close         | ; |  |  |  |  |

Figure 12: Z Fit window of impedance after compensation.

After compensation, the measured capacitance value matches the nominal capacitances given by the manufacturer.

### **IV-3 DISCUSSION**

It was shown that when the DUT capacitance is smaller than, or comparable in magnitude to, the cables or/and sample holder capacitance (100 pF capacitor) the impedance measurements are not reliable and a compensation is needed. This compensation is also needed even for relatively high capacitance DUT especially when a high accuracy is requested. Indeed, a second test was performed on a 10.00 nF capacitor (around 100 time higher than the cables capacitance) to check the effect of compensation on relatively high capacitance. A 10.18 nF capacitance value was measured without compensation. After compensation a

IIIII

capacitance of 10.05 nF was obtained. So, even for high capacitance values, the compensation is recommended for optimum accuracy. The compensation could be ignored for very high capacitances when a high accuracy is not requested.

For accurate and repeatable measurements, the open circuit, sort circuit and probably load compensation have to be performed exactly in the same conditions as that on the DUT.

Table 1 below summarizes the measured capacitances of two capacitors (with nominal capacitance of 100 pF and 10 nF) with and without compensation.

Table 1: Measured capacitances obtained with andwithout compensation.

| DUT                 | 100 pF | 10 nF    |

|---------------------|--------|----------|

| Nominal capacitance | 100 pF | 10.00 nF |

| Capacitance without |        |          |

| compensation        | 223 pF | 10.18 nF |

| Capacitance with    |        |          |

| compensation        | 99 pF  | 10.05 pF |

#### Note: Compensation vs. Calibration

The accuracy of a measuring instrument (LCR, impedance analyzer, etc) is specified by the manufacturer in the Impedance contour plot [7]. The accuracy is given at the BNC connectors which define the "Calibration Plane" or the reference plane. The instrument is calibrated up to BNC connectors. The use of cables and or a sample holder alters the the instrument accuracy of and а compensation procedure is needed to compensate for residual impedances introduced by the cables and or the sample holder.

A potentiostat can also be used for measuring electrical properties of a DUT. A potentiostat is mainly calibrated up to the end of the cables so a compensation is needed when a sample holder is used.

# **V- CONCLUSION**

Impedance measurement performed on 100 pF and 10 nF capacitors showed residual

capacitances induced by cables. The compensation has eliminated these residual impedances. This compensation is almost always necessary to compensate for residual impedances due to cables and/or sample holder. After compensation, the measured capacitances match the nominal capacitances given by the manufacturer.

## REFERENCES

1) Agilent Impedance Measurement Handbook, a guide to measurement technology and techniques, 4<sup>th</sup> edition.

2) B. J. Christensen, R.T Coverdale, R. A. Olsen, S.J. Ford, E.J. Garboczi, H. M. Jennings, T. O. Mason, J. Am. Ceram. Soc, 77 (1994), 2789.

3) S.J. Ford, T.O. Mason, B.J. Christensen, R.T. Coverdale, H.M. Jennings and E.J. Garboczi, J. Mater. Sci. 30(5), (1995) 1217.

4) <u>Technical note #1</u> Cell cable and sample holder compensation.

5) E. Barsoukov, J. Ross Macdonald, John Wiley & Sons, (2005), chap 3, 184.

6) <u>Technical note #5</u> Which connection to use with MTZ-35.

7) <u>Application note #54</u> How to read EIS accuracy contour plots.

Science Instruments, 4 Rue de Vaucanson, 38170 Seyssinet-Pariset, FRANCE Tel: +33 476 98 68 31 – Fax: +33 476 98 69 09 <u>www.bio-logic.net</u>

Marres